## JPE 8-3-9

# A Novel Two Phase Interleaved LLC Series Resonant Converter using a Phase of the Resonant Capacitor

Kang-Hyun Yi\* and Gun-Woo Moon<sup>†</sup>

<sup>†\*</sup>School of Electrical Engineering and Computer Science, Division of Electrical Engineering, KAIST

## ABSTRACT

An LLC series resonant converter has many unique characteristics and improvements over PWM topologies. However, many output capacitors are needed in parallel to satisfy output voltage ripple and the rated ripple current of the capacitors. This paper deals with a novel two phase interleaved LLC resonant converter using a phase of the resonant capacitor. The proposed converter can satisfy output voltage ripple and a rated ripple current of capacitors with few output capacitors, relatively. The operation and features are considered in detail and a prototype with a 12V-100A output is investigated.

Keywords: LLC series resonant converter, Phase of the resonant capacitor, Interleaving operation

### 1. Introduction

Due to high power density requirements, high frequency DC/DC power converters are employed increasingly in many applications. People are paying more attention to the LLC series resonant converter (LLC-SRC), owing to its many unique characteristics and improvements over previous PWM converters. For example, it has simple structure and can achieve primary MOSFETs' zero voltage switching (ZVS) and the secondary rectifiers' zero current switching (ZCS) from no load to full load <sup>[1-3]</sup>. However, many output capacitors are needed in parallel in the conventional LLC-SRC to satisfy output voltage ripple and the rated ripple current of capacitors because the secondary current is discontinuous and the peak current value is large. In addition, this problem is very serious in

high current output applications. Although high frequency operation can be a solution for reducing the output capacitance, many capacitors in parallel are still needed to satisfy the rated ripple current of the output capacitor.

An interleaved operation can be the solution to this drawback but a complex controller is needed to obtain the interleaving operation in the prior approach <sup>[4]</sup>. In this paper, a new interleaved LLC-SRC without the complicated controller is proposed. It is suitable for low-voltage and high-current applications which use a synchronous switch to reduce the Schottky diode's conduction loss. The interleaved operation in the proposed converter can be easily obtained without the complex controller because it uses a phase of the resonant capacitor. Furthermore, the output capacitor and the conduction loss can be reduced by the interleaved operation. As a result, the proposed converter can achieve high efficiency, high power density and low cost. The method of using a phase of the resonant capacitor can be extended to make a multi-phase interleaved LLC-SRC.

Manuscript received April 10, 2008; revised June 2, 2008 <sup>†</sup>Corresponding Author: gwmoon@ee.kaist.ac.kr

Tel: +82-42-869-3475, Fax: +82-42-869-8520, KAIST

<sup>\*</sup>Division of Electrical Engineering, KAIST

## 2. The proposed converter

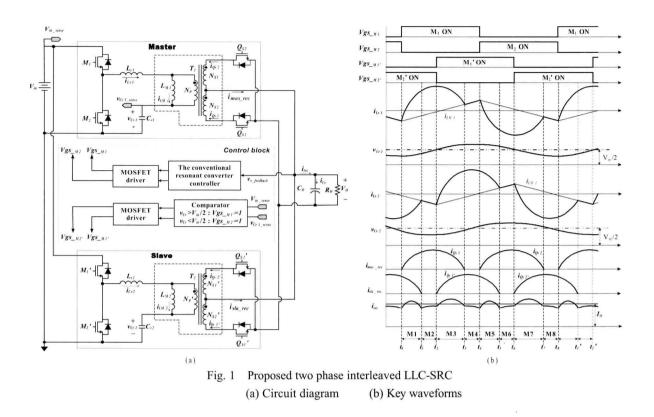

Fig. 1 shows the circuit diagram and key waveforms of the proposed two phase interleaved LLC-SRC. The proposed converter is composed of two half-bridge LLC-SRCs; one is the master converter and the other is the slave converter. The gate signals of the MOSFET in the master converter are made by the conventional controller to regulate the output power, and the gate signals of the slave converter are made by a phase of the resonant capacitor,  $C_{rl}$ , voltage in the master converter as shown in Fig. 1 (a). Since the phase between the resonant inductor current and the resonant capacitor voltage has 90 degree difference, the interleaving operation in the master and the slave converters can be easily obtained by detection of the phase of the resonant capacitor voltage,  $v_{Crl}$ . The operational principle of the proposed circuit can be explained as follows. The operation of the proposed circuit can be divided to eight modes. Since M1~M4 and M5~M8 are symmetric, only the operation from M1 to M4 will be explained. It is assumed that the components in the master and slave converter are ideally the same.

**Mode 1(t<sub>0</sub>~ t<sub>1</sub>)**: Switches,  $M_1$  and  $M_2'$ , have been turned on and the energy is transferred from input to output by the master and slave converter. The inductor currents can be expressed as follows

$$\begin{split} i_{Lr1}(t) &= I_{Lr1}(t_0) \cos \frac{1}{\sqrt{L_{r1}C_{r1}}} (t-t_0) \\ &+ \left( V_{in} / 2 - V_{Cr1}(t_0) \right) / \sqrt{\frac{L_{r1}}{C_{r1}}} \sin \frac{1}{\sqrt{L_{r1}C_{r1}}} (t-t_0) \\ i_{Lr2}(t) &= I_{Lr2}(t_0) \cos \frac{1}{\sqrt{L_{r2}C_{r2}}} (t-t_0) \\ &- \left( V_{in} / 2 - V_{Cr2}(t_4) \right) / \sqrt{\frac{L_{r2}}{C_{r2}}} \sin \frac{1}{\sqrt{L_{r2}C_{r2}}} (t-t_0) \\ \end{split}$$

(2)

where  $I_{Lr1}(t_0) = I_{Lr2}(t_0) = I_{Lm,peak}$ .

**Mode 2(t<sub>1</sub>~ t<sub>2</sub>):** The master converter only transfers the energy to the output because the resonance between  $L_{r2}$  and  $C_{r2}$  has been completed in the slave converter. The primary currents can be obtained as follows.

$$i_{Lr1}(t) = I_{Lr1}(t_0) \cos \frac{1}{\sqrt{L_{r1}C_{r1}}} (t - t_0)$$

$$+ \left( V_{in} / 2 - V_{Cr1}(t_0) \right) / \sqrt{\frac{L_{r1}}{C_{r1}}} \sin \frac{1}{\sqrt{L_{r1}C_{r1}}} (t - t_0)$$

(3)

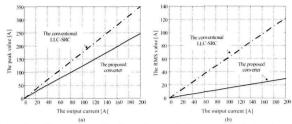

Fig. 2 Comparison in the prior and the proposed circuit (a) The peak value of the rectified current (b) The RMS value of the output capacitor ripple current

$$i_{Lr2}(t) = I_{Lr2}(t_1) \cos \frac{1}{\sqrt{(L_{r2} + L_{m2})C_{r2}}} (t - t_1) - V_{Cr2}(t_1) / \sqrt{\frac{(L_{r2} + L_{m2})}{C_{r2}}} \sin \frac{1}{\sqrt{(L_{r2} + L_{m2})C_{r2}}} (t - t_1)$$

(4)

Mode  $3(t_2 \sim t_3)$ : When the  $v_{Cr1}$  is over  $V_{in}/2$  in the master converter, the M1' switch is turned on and the output is also made by the slave converter with the master converter.

$$i_{Lr1}(t) = I_{Lr1}(t_0) \cos \frac{1}{\sqrt{L_{r1}C_{r1}}} (t-t_0)$$

$$+ (V_{in} / 2 - V_{Cr1}(t_0)) / \sqrt{\frac{L_{r1}}{C_{r1}}} \sin \frac{1}{\sqrt{L_{r1}C_{r1}}} (t-t_0)$$

$$i_{Lr2}(t) = I_{Lr2}(t_2) \cos \frac{1}{\sqrt{L_{r2}C_{r2}}} (t-t_2)$$

$$+ (V_{in} / 2 - V_{Cr2}(t_2)) / \sqrt{\frac{L_{r2}}{C_{r2}}} \sin \frac{1}{\sqrt{L_{r2}C_{r2}}} (t-t_2)$$

(6)

Mode  $4(t_3 \sim t_4)$ : Since the resonance between  $L_{r_1}$  and  $C_{r_1}$ is finished in the master circuit, only the slave converter transfers the energy to the output.

$$i_{Lr1}(t) = I_{Lr1}(t_3) \cos \frac{1}{\sqrt{(L_{r1} + L_{m1})C_{r1}}} (t - t_3) + (V_{in} - V_{Cr1}(t_0)) / \sqrt{\frac{(L_{r1} + L_{m1})C_{r1}}{C_{r1}}} \sin \frac{1}{\sqrt{(L_{r1} + L_{m1})C_{r1}}} (t - t_3) i_{Lr2}(t) = I_{Lr2}(t_2) \cos \frac{1}{\sqrt{L_{r2}C_{r2}}} (t - t_2) + (V_{in} / 2 - V_{Cr2}(t_2)) / \sqrt{\frac{L_{r2}}{C_{r2}}} \sin \frac{1}{\sqrt{L_{r2}C_{r2}}} (t - t_2)$$

(8)

The primary switches in the slave converter are easily driven by comparison between the input and the resonant capacitor voltages in the master converter. Furthermore,

Specific Components of a Prototype Table 1 Value /Part Symbol Parameter Input voltage 410 V V. Output voltage V<sub>o</sub> 12 V 1200 W Max . power rating Pman N.:N.:N. 16:1:1 Turn ratio L.L. 25 uH Resonant inductor 1 mH Magnetizing inductance L. L. Cr.Cr 63 nF /600 V capacitor Resonant Output capacitance c. 330 uF /(16 V, 6.1 Arms )(4 EA ) M 1. 2. 17. 2\* SPP 20 N 60 C 3 Primary switches Q ,1, ,2, ,1', ,2' IRF 2804 (2 EA ) Synchronous rectifier Synchronous rectifier drive IR 21167 MC 33067 Resonant mode controlle

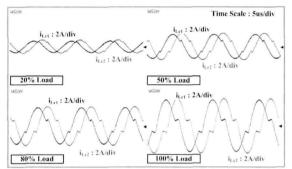

Fig. 3 The resonant inductor current with the load variation

different from the conventional LLC-SRC, the current,  $i_{rec}$ , is continuous in the proposed converter as shown in Fig. 1. This results in the reduction of output voltage ripple and a root mean square (RMS) value of the output capacitor's ripple current. The peak value of the rectified current and the RMS values of the output capacitor's ripple currents of the conventional full-bridge LLC-SRC and the proposed converter can be obtained during half of the switching period as follows

$$I_{Conventional\_rec\_pk} \cong \frac{T_s}{T_r} \frac{\pi}{2} I_o$$

(9)

$$I_{Conventional\_Co\_RMS} \cong I_o \sqrt{\left(\frac{\pi^2}{8} \frac{T_s}{T_r} - 1\right)}$$

(10)

$$I_{Proposed\_rec\_pk} \cong \frac{T_s}{T_r} \frac{\pi}{4} \sqrt{2} I_o \tag{11}$$

$$I_{Proposed\_Co\_RMS} \cong I_o \sqrt{\left(\frac{\pi^2}{16} \frac{T_s}{T_r} \left(1 + \frac{2}{\pi}\right) + \frac{T_r}{T_s} - 2\right)}$$

(12)

where  $T_s$  is the switching period,  $T_r$  is the resonant period and  $\omega_r$  is  $2\pi/T_r$ .

By (9)-(12), the peak value of the rectified current and the RMS value of the output capacitor's ripple current can

Fig. 4 The waveform of the ripple output voltage

be obtained according to the output current as shown in Fig.2. Fig. 2 illustrates that the proposed circuit has the greatly reduced peak value of the rectified current and the RMS value of the output capacitor current. Since the RMS value of the output capacitor ripple current will not be decreased with high frequency operation, many electrolytic capacitors are needed in parallel to satisfy the rated ripple current of the output capacitor in the conventional LLC-SRC. However, since the rectified current of the proposed circuit is continuous, the peak value of the rectified current, the ripple current and the RMS value of the output capacitor are small, respectively. Thus, the proposed circuit can have fewer output capacitors and smaller conduction losses in the transformer and the synchronous MOSFET. Therefore, the proposed circuit can obtain high power density, high efficiency and low cost.

#### 3. Experimental results

A prototype of a 12V, 1.2kW converter with 410V input has been built for the application of the distributed power system of a server computer. The components are shown in table 1. The primary switches in the master converter are driven by the controller, which is used to regulate the output power and those in the slave converter are simply driven by comparison between the input voltage and the resonant capacitor voltage of the master converter. Fig. 3 shows the resonant inductor currents in the master and slave converter with the load variation. It is noted that the phase difference between the master's inductor current and the slave's is about 90 degree and the input power is well divided to make the output power in the master and slave converts. Fig.4 shows the ripple output voltage

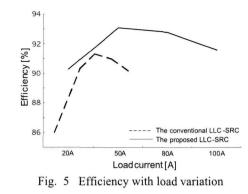

capacitors in the 100A load. The peak to peak value of this, due to the interleaving operation, is about 40mV with the four output capacitors. Also, since the RMS value of the output capacitor current is small, only 4 capacitors are needed to satify the rated ripple current of the electrolytic capacitor, while the conventional LLC needed about 12 capacitors. Fig 5 shows the efficiency of the proposed circuit according to the load variation. From light load to full load, the proposed converter has a high efficiency over 90%. Using the phase of the resonant capacitor, the interleaved operation can be easily obtained without the complicated controller. Due to this concept, the proposed LLC-SRC can have fewer output capacitors, higher efficiency and higher power density.

#### 4. Conclusion

The proposed converter utilizes interleaved operation using a phase of the resonant capacitor instead of a complex controller. It also significantly reduces the RMS value of the output capacitor's current and the peak current value on the secondary side. This results in reducing the number of output capacitors. Moreover, the method of using a phase of the resonant capacitor voltage can be extended to make a multi-phase interleaved LLC-SRC. Therefore, it is suitable for low voltage and high current applications that require high efficiency, high power density and low cost, such as server and telecommunications equipment.

#### References

Bo Yang, and Fred.C.Lee, "LLC Resonant converter for Front End DC/DC Conversion", *IEEE APEC*, pp.1108-1112, 2002.

- [2] Hang-Seok Choi, "Design Consideration of Half-Bridge LLC Resonant Converter", *Journal of power electronics*, Vol. 7, No.1, pp. 13-20, Jan. 2007.

- [3] Gwang-Taek Lee, Darl-Woo Lee, Tae-Young Ahn, Sung-Cheol Kim, Chan-Gyu Jang, "A study on the LLC resonant Half-bridge converter that use current comparison type synchronous rectifier", *Proceeding of KIPE 2005 Fall Annual Conference*, pp. 117-120, 2005.

- [4] Taotao Jin and Keyue Smedley, "Multiphase LLC Series Resonant Converter for Microprocessor Voltage Regulation", in Proc. IEEE 41st IAS Annual Meeting. Conference, pp. 2136-2143, 2006.

Kang-Hyun Yi (S'05) Kang-Hyun Yi was born in Korea, in 1978. He received the B.S. degree in the Electrical Engineering from Hanyang University, Seoul, Korea in 2003 and the M.S. degree in Electrical Engineering and Computer Science from the KAIST,

Daejeon, Korea in 2006. He is currently working toward a Ph.D. degree in Electrical Engineering from the KAIST, Daejeon, Korea. His main research interests are high efficiency plasma display panel (PDP) driver circuits, DC/DC converters, soft switching techniques, and digital display drivers. Mr. Yi is a member of the Korean Institute of Power Electronics (KIPE).

Gun-Woo Moon (S'92-M'00) received the M.S. and Ph.D. degrees in Electrical Engineering from the KAIST, Daejeon, in 1992 and 1996, respectively. He is currently an Associate Professor in the department of Electrical Engineering, KAIST. His research

interests include modeling, design and control of power converters, soft-switching power converters, resonant inverters, distributed power systems, power-factor correction, electric drive systems, driver circuits of plasma display panels, and flexible ac transmission systems. Dr. Moon is a member of the Korean Institute of Power Electronics (KIPE), the Korean Institute of Electrical Engineers (KIEE), the Korea Institute of Telematics and Electronics (KITE), the Korea Institute of Illumination Electronics and Industrial Equipment (KIIEIE), and the Society for Information Display (SID).